## **High-K Dielectrics / High-Mobility Channel MOSFETs**

Jack C Lee, The University of Texas at Austin September 21, 2012 Puebla 's IEEE CAS and EDS Chapters National Institute for Astrophysics, Optics and Electronics

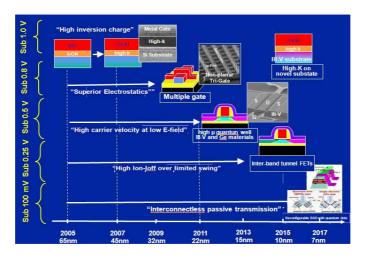

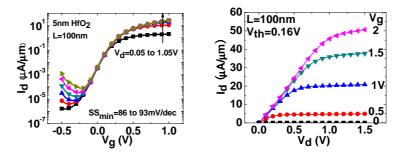

High-K dielectrics such as HfO<sub>2</sub>, ZrO<sub>2</sub> and HfSiON have attracted a great deal of attention for reduced power dissipation in CMOS applications. However, channel mobility degradation, charge trapping and reliability are major concerns. In this paper, we will review recent research results, e.g. the charge trapping characteristics, the effects of nitrogen on channel mobility. More recently high channel materials such as III-V, Ge and graphene with high-K dielectrics are attractive for achieving enhanced device performance for MOSFETs (Fig.1). To achieve high performance III-V n-MOSFETs, we have systematically investigated the effect of process annealing sequence, channel thickness/doping concentration and high-K gate stacks on device performance of surface channel InGaAs MOSFETs. High performance In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFETs with optimized device structure and process will be presented. To further improve the channel mobility, we have also studied buried channel InGaAs MOSFETs with InP or InP/InAlAs barrier layers. We will also present our work on substrate structure optimization and mobility scattering mechanism on buried channel III-V MOSFETs. Highest channel mobility of ~5000 cm<sup>2</sup>/Vs has been achieved by using In<sub>0.7</sub>Ga<sub>0.3</sub>As channel with InP/InAlAs doublebarrier and ALD Al<sub>2</sub>O<sub>3</sub> oxide. Band gap engineering and gate stack scaling were applied to In<sub>0.7</sub>Ga<sub>0.3</sub>As vertical tunneling FET (TFETs) with lower SS (86mV/dec) and higher  $I_d$  ( $50\mu\text{A/}\mu\text{m}$ ) vs. previously reported data (Fig. 2).

Fig. 1: High-mobility channel (e.g. III-V materials) MOSFETs and tunnel FETs are to be incorporated into CMOS in the near future [Source: Intel].

Fig. 2: The smallest subthreshold swing of 86 mV/dec and  $I_{on}$  of 50 mA/mm at  $V_g$ =2 V was achieved by TFETs with 5 nm HfO<sub>2</sub> (EOT=1.2 nm). The gate leakage current is less than  $1\times10^{-4}$  A/cm<sup>2</sup> at  $V_g$ =1 V.