# **LATW**2008

9thIEEELatin-AmericanTestWorkshop

Puebla, Mexico

February 17 - 20, 2008

## General Chairs:

V. Champac - INAOE, Mexico

champac@inaoep.mx Y. Zorian – Virage Logic Corp., USA yervant.zorian@viragelogic.com

R. Murphy - INAOE, Mexico

Program Chairs: M. Lubaszewski - UFRGS, Brazil

#### R. Velazco - TIMA, France

**Embedded Tutorials Chairs:**

#### J. Calvano - Braz. Navy, Brazil

Z. Peng-Linköping Univ., Sweden Panels Chair: M. Abadir – Freescale, USA

#### L.Carro - UFRGS. Brazil

#### Finance Chair:

F. Vargas - PUCRS, Brazil

Publicity Chairs:

J. Huertas - IMSE/CNM, Spain

R.Reis - UFRGS, Brazil

#### Publication Chair:

Miguel Gutierrez de A., INAOE. Mexico

#### Industry Liaison:

G. Espinosa, Freescale, Mexico

#### **IEEE D&T Liaison:**

K. Roy - Purdue Univ., USA

TTEP Tutorials Liaison:

D.Gizopoulos - Univ. Piraeus, Greece

#### West Europe Liaison:

M. Flottes - LIRMM, France

East Europe Liaison:

#### R. Ubar - Talin Tech. Univ., Estonia North-America Liaison:

J. Abraham, Univ. Texas, USA

#### Program Committee:

J. Abraham, Univ. Texas, USA

# V. D. Agrawal, Auburn Univ., USA L. Anghel, TIMA, France F. Azaïs, LIRMM, France

V. Avendano, Freescale, Mexico L. Balado, UPC, Spain

A. Brun, Univ. Paris-Sud, France

A. Chatterjee, Georgia Tech., USA

E. Cota, UFRGS, Brazil

E. Duarte Junior, UFPR, Brazil

A. Diaz-Mendez, INAOE, Mexico

C. Dueñas, Freescale, Brazil

A. O. Fernandes, UFMG, Brazil J. Figueras, UPC, Spain P. Fouillat, CNFM, France

J. L. Guntzel, UFPEL, Brazil J. P. de Gyvez, NXP, The Netherlands J. Hayes, Univ. Michigan, USA

C. F. Hawkins, UNM, USA

A. Ivanov, Univ. British Columbia, Canada

D. Lupi, INTI, Argentina

E. J. Marinissen, NXP, The Netherlands

Y. Mita, Univ. Tokyo, Japan F. Moraes, PUCRS, Brazil G. Peretti, UTN-FR Villa Maria, Argentina

. Perez, UROU, Uruguay . Rayas-Sanchez, ITESO, Mexico

E. Romero, UTN-FR Villa Maria, Argentina

E. Rolleto, U IN-Fr Villa Maria, Afgentina A. Rueda, IMSE-CNM, Spain J. Segura, U. Illes Balears, Spain C. Silva, PUCP, Peru M. Soma, Univ. Washington, USA J. Sosnowski, Warsaw Univ. Techn., Poland

J. M. de Souza, FITec, Brazil

M. Strum - USP, Brazil J. Velasco-Medina, Univ. del Valle, Colombia

S. Vergilio, UFPR, Brazil T. Weber, UFRGS, Brazil A. Zenteno, Intel, Mexico

#### Steering Committee: V. Champac (Chair)

M. S. Lubaszewski (LA-TTTC Chair)

J. Huertas Vargas

R. Velazco

### Call for Papers

The IEEE Latin-American Test Workshop provides an annual forum for test and fault tolerance professionals and technologists from Latin America and all over the world to present and discuss various aspects of system, board and component testing and fault-tolerance with design, manufacturing and field considerations in mind. The best papers presented at the 9th LATW will be invited for submission to the IEEE Design and Test of Computers and Journal of Integrated Circuits and Systems.

## Topics of interest include but are not limited to: - Analog Mixed Signal Test - 1

- Automatic Test Generation

- Board and System Test

- Built-In Self-Test

**Defect-Based Test**

- Dependability

- Design and Synthesis for Testability

Design Verification/Validation

**Design for Manufacturability**

- Economics of Test

- Fault Analysis and Diagnosis

- Fault Modeling and Simulation

- Fault-Tolerance in HW/SW

- Fault-Tolerant Architectures

Memory Test and Repair

On-Line Testing

Process Control and Measurements

Raoul Velazco raoul.velazco@imag.fr

- Radiation Hardening Techniques

- System-on-Chip Test

- Yield Optimization

#### **Topic Coordinators:**

Analog and Mixed-Signal - M. Renovell, LIRMM, France

DfT & BIST - A. Orailoglu, UC San Diego, USA

On-line Test and Fault Tolerance - D. K. Pradhan, University of Bristol, UK

Space Radiation - F. Lima, UFRGS, Brazil

Verification and High Level Test - M. Reorda, Politecnico di Torino, Italy

Software Testing - E. Bezerra, PUCRS, Brazil

#### **Paper Submission Information:**

Those interested in presenting recent results at the workshop are invited to submit either an extended abstract, one to three pages long, or a full length paper. PDF electronic submissions should be done via the workshop webpage: http://latw.tttc-events.org/. Authors should send papers in the IEEE format with a cover letter indicating the complete mail address, phone/fax numbers and e-mail addresses, the contact person and the presenter. Detailed instructions are available at the workshop webpage. The Program Committee also welcomes proposals for panels and special topic sessions. For additional information please contact one of the Program Co-Chairs.

Marcelo Lubaszewski luba@ece.ufrgs.br

**Submission deadline:** November 1st, 2007 Notification of acceptance: December 10th, 2007 **January 10th, 2008** Camera Ready:

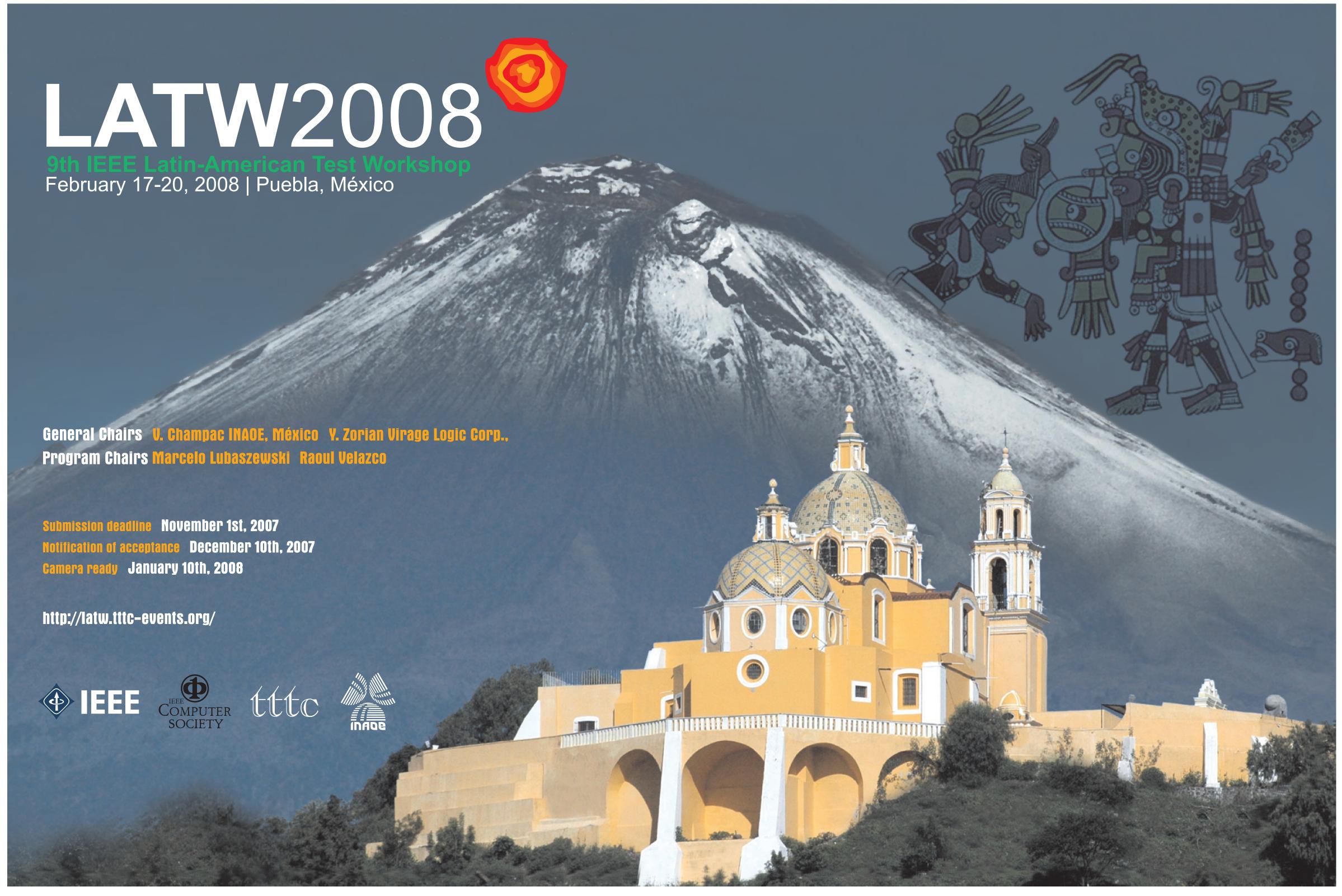

ATW2008 will be held in Puebla, Mexico. Puebla is also known as the City of Angels, a World Heritage City, lies 136 km (84 miles) from Mexico City. Puebla, a city of gray hewn stone constructions, is Mexico's fourth largest city. Walking along the streets, you will see marvelous facades with lovely iron balconies, traditional markets and beautiful plazas. Here you will find wonderful crafts, including Talavera pottery, the tree of life figurines, bark paper paintings and unique onyx and marble sculptures. Near Puebla you can visit the Izta-Popo National Park, La Malinche National Park and the Valle de Tehuacan Biosphere Reserve, the largest reserve in the world. From Puebla you can reach interesting ancient places. Among them Cholula Pyramid, Cacaxtla (where you can still admire mural painting), pyramids of Teotihuacan and the site of Monte Alban (Oaxaca).

**Sponsored by:** IEEE Computer Society Test Technology Technical Council (TTTC) Organized by: National Institute for Astrophysics, Optics and Electronics, INAOE